KI SPEED

KI zur Leistungssteigerung von SiC Power Elektronik durch Defektreduktion

Forschungsgebiet:

- Laufzeit:

- 01.04.2024 - 31.03.2028

- Projektstatus:

- laufend

- Einrichtungen:

- Fakultät für angewandte Naturwissenschaften und Mechatronik

- Projektleitung:

- Prof. Dr. Alfred Kersch, Prof. Dr. Ney Moreira

- Förderprogramm:

- Forschung an Fachhochschulen in Kooperation mit Unternehmen (FH-Kooperativ)

- Drittmittelart:

- Bund, Private Dritte

- Projektart:

- Forschung

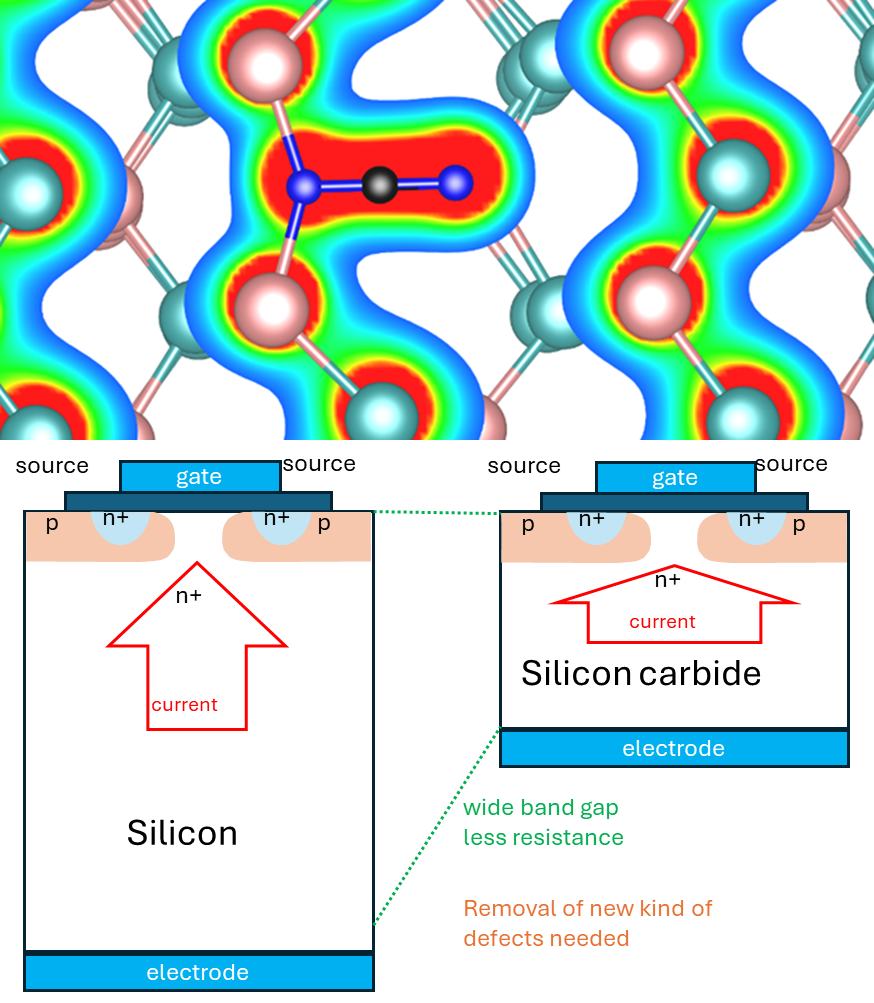

Das übergeordnete Ziel des Projektes ist die Weiterentwicklung von Siliziumcarbid (SiC) Prozessen für die Hochleistungselektronik, welche in der Energie- und Mobilitätswende eine Schlüsselrolle spielt. Die Effizienz dieser Bauelemente ist durch die hohe Defektdichte an SiC-SiO2 Grenzflächen beeinträchtigt. In dem Vorhaben sollen die prozessbedingten Ursachen dieser Defekte fundamental und mit neuartigen Simulationsmethoden aufgeklärt werden. Die Systemgröße in Raum und Zeit ist in bisherigen Untersuchungen mit first-principles Methoden durch den hohen Rechenaufwandes limitiert. Daher soll in dem Vorhaben die Systemgröße durch Methoden der künstlichen Intelligenz KI wesentlich vergrößert werden. Dies geschieht durch das maschinelle Lernen des Energie-Potentials der atomaren Wechselwirkung anhand von Si / C / O Trainings-Strukturen, die mit first-principles Methoden berechnet werden. In einer zweiten Stufe wird dieses Potential auf Si / C / O / N / H Teststrukturen erweitert, um Defektpassivierung durch Stickstoff und Wasserstoff untersuchen zu können.

Das maschinelle Lernen der Potentiale geschieht mit der Deep Potential Methode und dem frei verfügbaren DeepMD, die Molekulardynamik-Simulation der Prozesse auf einem Multi-Core PC mit Grafikkarten. Die Systemgröße der Grenzfläche wird um drei Größenordnungen erweitert. In der Prozessimulation wird die Entstehung der Defekte in Abhängigkeit von Temperatur, N und H Angebot simuliert. Die strukturellen Eigenschaften identifiziert und ihre elektronischen Eigenschaften mit first-principles Methoden ausgewertet. Die Daten zu möglichen Prozessverläufen sowie zu realen Grenzflächen werden von Infineon zur Verfügung gestellt. Die Ergebnisse werden in regelmäßigen Projektmeetings vorgestellt und gemeinsam mit Infineon interpretiert. In der letzten Phase des Vorhabens wird das atomare SiC-Modell für Modellierung von Wachstumsprozessen der SiC-Wafern verwendet, wobei hier das Ziel die Vermeidung von Defekten ist.

Projektförderung