Scale4Edge

Skalierbare Infrastruktur für Edge Computing

Projektleiter:in

Laufzeit: 01.01.2024 - 31.12.2025

Projektträger: VDI/VDE/IT Berlin

Partner: AbsInt Angewandte Informatik GmbH Saarbrücken, EPOS GmbH DV-Consult & Training Bremen, Rheinland-Pfälzische Technische Universität Kaiserslautern-Landau (RPTU), SpiNNcloud Systems GmbH Dresden, Universität Bremen, Universität Paderborn, edacentrum GmbH Hannover, Albert-Ludwigs-Universität Freiburg, Deutsches Zentrum für Luft- und Raumfahrt e.V. Köln, Eberhard Karls Universität Tübingen, FZI Forschungszentrum Informatik Karlsruhe, IHP GmbH – Innovations for High Performance Microelectronics/Leibniz-Institut für innovative Mikroelektronik Frankfurt (Oder), MINRES Technologies GmbH Neubiberg, Robert Bosch GmbH Gerlingen, SYSGO GmbH Klein-Winternheim, Technische Universität Darmstadt, Technische Universität Dresden, Technische Universität München

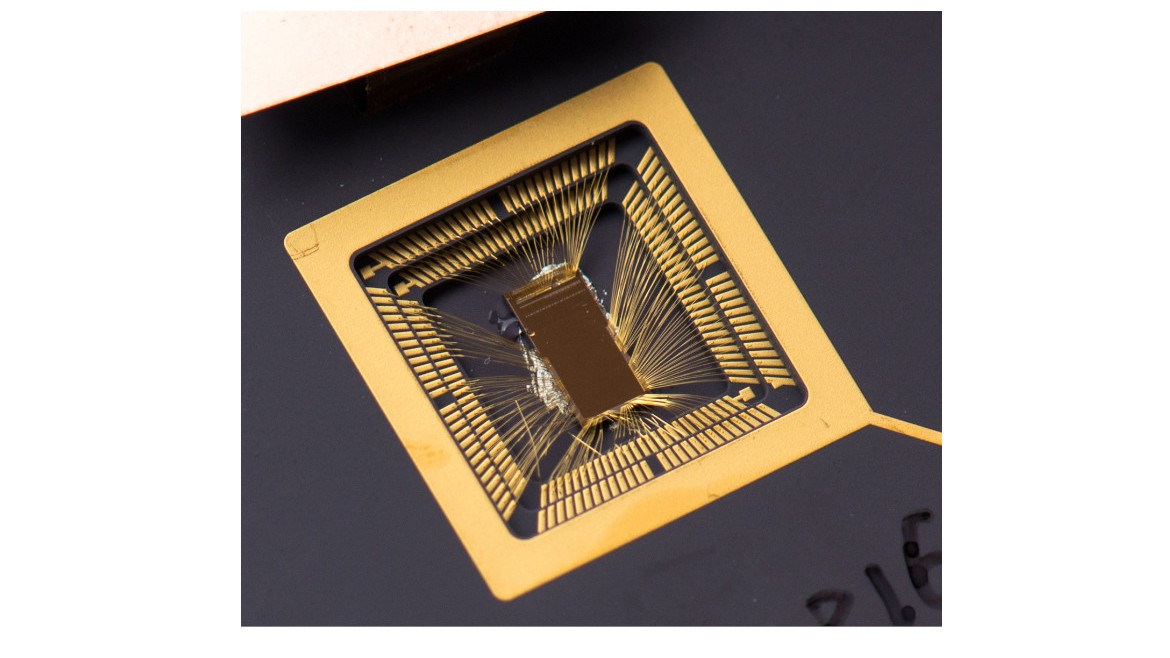

Scale4Edge stellt ein Ökosystem für eine skalierbare und flexibel erweiterbare Edge-Computing-Plattform bereit, welches auf der freien RISC-V-Instruktionssatzarchitektur basiert. In dem Projekt forscht die HM an hochoptimierten Prozessoren mit niedrigem Speicherbedarf.

Scale4Edge stellt ein Ökosystem für eine skalierbare und flexibel erweiterbare Edge-Computing-Plattform bereit, welches auf der freien RISC-V-Instruktionssatzarchitektur basiert. Das Ökosystem bietet eine skalierbare, maßgeschneiderte Komplettlösung einschließlich Support. Hierzu gehören auch standardkonforme Entwurfsprozesse, teilweise quelloffene Software und ebenso die Sicherheit (Safety, Security) der Plattform sowie eine intensive Überprüfung und Analyse der Entwicklungen. Die RISC-V-Plattform des Ökosystems stellt dem Anwender drei Ebenen für die Implementierung zur Verfügung: (1) CPU-Instruktionsebene, festgelegt durch den RISC-V-ISA-Standard, (2) Software-Ebene, festgelegt durch den C-Standard und ergänzende Standards wie MISRA-C, und (3) Betriebssystemebene mit Systemdiensten, Ressourcenallokationen und Konfigurationsschnittstellen. Die zweite Projektphase dient der Optimierung und der Entwicklung zusätzlicher Komponenten für eine erfolgreiche Bereitstellung des Ökosystems.

Die Hochschule München (HM) tritt dem Konsortium in der zweiten Phase bei, um mit der Expertise in effizienten Befehlssatzerweiterungen an Open-Source RISC-V Prozessoren und die Vernetzung im internationalen RISC-V Umfeld das Konsortium weiter zu verstärken. Dabei stehen neben den technischen Arbeiten an Befehlssatzerweiterungen zur Verbesserung der Codegröße in ressourcenbeschränkten Systemen auch die gezielte Teilhabe an den globalen Standardisierungsaktivitäten, sowie die Koordination der technischen Beiträge einer Roadshow im Vordergrund.

Zuwendungsgeber: